本集研究员:青工所宁超

「芯片还会进步吗?科技是不是停滞了?算力被锁死了吗?半导体还有希望吗?」

2023 年 8 月,面对我敬仰已久的龙芯 CPU 首席科学家胡伟武,我抛出了自己许久的疑惑。

没想到,胡伟武笑了,「你这个假设不成立,关键是有些物理学的定理给你限制住了」,随即他又严肃道,「我认为摩尔定律实际上是已经到头了」。

所以,芯片好像确实出问题了。

疑问的诞生

芯片为什么不进步了?

这个问题看起来有些不合时宜,又有一些杞人忧天。但它们的的确确是从我成长轨迹里长出的疑问。

- 1995 年, 我出生于处理器芯片术兴起的时代。那一年,图形化界面操作系统与奔腾处理器诞生。

- 1998 年,家里买了一台电脑,是卧式的金长城。

- 2000 年, 我第一次用电子琴,玩红白机,玩 Gameboy。

- 2002 年,我第一次看到 MP3,液晶屏幕。

- 2006 年,家里的大人用上了笔记本电脑,手里拿着诺基亚手机。

之后,家里每年都有值得兴奋的玩意。就像《越来越好》这首歌里唱到的那样:「房子大了,电话小了,感觉越来越好……」

我很想知道,是什么让这一切越来越好?我不停地拆,发现答案就在一个个小方块上——芯片。 于是,2014 年,我大学学了半导体专业,进入黄昆班,正式开始专业课的学习。(注:黄昆班是以我国著名的物理学家和教育家黄昆先生命名,由北京科技大学与中国科学院半导体研究所合作办学。)但从我进入学校开始,这一切就变了。屏幕、电脑、手机,千篇一律,我们的技术好像就定格在了我进入大学那天。

2018 年,我毕业。班里 18 个人,只有一个人进入芯片相关的领域,芯片专业好像也不需要那么多人。毕业后,我找了些为了生活的工作。去酒吧兼职,学过调酒;去新东方做物理老师;去新媒体从事过文稿工作……2022 年,失业。

我一直想不明白,为什么这么多年没有值得兴奋的新玩意儿了?我们的科技进步和这些芯片一样,似乎已经进入到了一个挤牙膏的时代。

2023 年 3 月,我来到《青工所》,这个不关乎我生活的问题终于有了发挥的契机。

关于算力

这一切要先从算力开始讲起。算力的意思很简单,就是计算的能力,指每秒能处理的次数。今天的人们用 OPS(Operations Per Second)来衡量算力的大小,1 OPS 就代表了每秒计算 1 次。更形象一点来说,你用一个计算器一秒按一次,就相当于 1 OPS。今天一枚芯片的算力最多能达到千万亿,每一秒都相当于铺满 5 个四川省的计算器在同时计算。

看起来很多,有什么问题是每秒千万亿次的计算解决不了的呢? 那可太多了,1000 万亿 OPS 甚至无法预测一杯水的运动。那能计算多少水呢?答案是:一滴水里面的一个大分子。这就是目前人类算力的极限。

一个拥有大算力的芯片里面,有超过百万个负责各类运算的模块。为了更好地理解,你可以把每一个运算模块想像成一台功能简单的「计算器」。

但这样的「计算器」还不是最小单位,如果我们再拆开一个「计算器」,就能看到 1000 左右的个晶体管,它们才是计算的最小单元,只能表示两个数字——0 和 1 。

你可能已经听说过,我们的手机电脑都是二进制,这就是二进制的本体,用 0 和 1 计算一切。提升算力,很大程度上就是把这些晶体管变小,这样,一块芯片里就能放下更多的「计算器」,拥有更大的算力。

所以,研究算力是否被锁死,我们得先找到晶体管。

寻找晶体管

在网络上,我们可以轻松搜到各种晶体管的图片,但它们都不好看,也无法表示真实情况下的晶体管结构。于是,我找了些更硬核的课程,在这些课程中,我看到了一张芯片最完整的样子,也就是这样的图纸,他们叫 GDS 版图。

但问题是,GDS 版图是芯片企业的最高机密,不容易找到。好在有很多硬核玩家 GitHub 上复刻了各种上世纪老芯片的版图,例如 Intel 4004,MOS 6502。打开一张版图,放大,最先映入眼帘的是纵横排布的线路,它们代表的是一层层导电的金属,晶体管就埋藏在这些金属的下面。

这些平面的图纸其实包含了三维信息。不同颜色代表不同高度,最上方的这些纵横的金属相当于电路中的导线。隐藏它们,露出来的就是芯片中最重要的部分——晶体管。

晶体管是一个开关,能在导电和绝缘两种状态之间反复横跳。决定是「开」还是「关」的东西是这里的电压。在处理器芯片中只有两种电压:高电压和低电压,也就是电脑中 1 和 0 。

电压是被加载在其中一条金属上的,它叫做栅极。一会导电一会绝缘的地方是下方的半导体,其实就是硅本身。硅里面被掺入了其他原子,根据掺杂的原子种类的不同,半导体的部分又被分为源极、漏极、衬底。

硅是怎么变成一个开关的?

由于掺入了不同的原子,源极、漏极的内部都是导电的,而它们之间的部分并不导电。

随着电压一点点被施加,中间不导电的区域表面会渐渐形成一个可以导电的地方,将源和漏导通在一起。这里就是导电沟道,虽然名字叫沟道,但它其实是半导体表面一个非常非常薄的可以导电的薄层。

通常,人们用导电沟道的长度代表晶体管的工艺,或者说晶体管有多小,比如 32 纳米工艺,说的就是这里。

研究到这,我找到了构成算力最基本的东西,晶体管——一个电压控制的开关,对应电脑中的信号 1 和信号 0。某种程度上,晶体管的数量决定了一张芯片的性能。

当开关的数量从 1 个变成 2000 个。

(图源:《青工所》S02E10)

300 万个——

(图源:《青工所》S02E10)

160 亿个——

(图源:《青工所》S02E10)

算力就这样诞生了。

今天,我同事每天都想用 AI 搞点事情,算力几乎就等于生产力,你我能同时使用的晶体管个数已经成为了一种资产。更强的算力意味着更多的晶体管,也就是更——大!

今天世界上最大的显卡变成了这样。晶体管的数量达到了 5 万亿个。这样看好像今天的算力并没有锁死,反而更强了。

但这件事太不对劲了。实际上,你并不能用这 5 万亿个晶体管来玩《显卡危机》,有资格使用这张巨大显卡的只有 Google Cloud、Meta、Microsoft 这几家公司。此去经年,那些让你眼前一亮的游戏,以及游戏之外关于未来的种种想象:在笔记本上训练一颗心智,在手机上预测一场台风,甚至量身定制一款药物,都不可能在你能拿在手里的设备上实现了。未来有资格干这些事的,可能依然是那几家大公司。

于是,我开始好奇,当算力以「巨物的形态拔地而起」究竟是意味着兴盛?还是一场算力的终结?

被垄断的巨物

| 电子管时代

这让我想起晶体管被发明前的时代。那时的算力,依赖于一个看起来很像电灯泡的东西——电子管。它也是一个电压控制的开关,在代表 0 或 1 的两种电压作用下,电子管内或是导电,或是关断。

在那个年代,更强的算力同样意味着「大」。更大的屋子,更多的机柜,就能同时放下数量更庞大的电子管,幽黄色的光芒下,好像每个人都有光明的未来。

真的是这样吗?

如果算力真的往「大」的方向发展,其实就意味着个人计算设备不存在了,没有笔记本电脑,没有手机,算力将不再属于个人,只能被大机构垄断和控制,但这并没有发生。事实上,仅仅是今天一台智能手机的算力,如果用电子管来实现,放不下,也造不完。制造这样一个电子管堆砌的巨物,将在空间上堆满整个地球,时间上堆满整个世纪。

只堆料增加晶体管数量,好像并不能拯救算力。

小一点,再小一点

| MOS管时代

四零年代的人们发现,如果仅靠堆数量不可行的话,那么打破个人算力锁死的办法就是找到一种能变得更小、更便宜、更省电的开关。

从物理上讲,电子管的体积、造价、功耗都不太可能持续地变小。所以,他们到死也不会「梦见」智能手机的诞生。电子管的时代天生就是一个算力被锁死的时代。

1960 年,贝尔实验室的默罕默德·马丁·阿塔拉和姜大元给出了解决算力锁死的答案——MOS 管,也就是我们开头提到的那个东西。准确地说,叫平面型晶体管,顾名思义,从上到下,导体,绝缘体,半导体,像三明治一样分层叠在一起。

世界上的晶体管很多,变小的最大限制是发热,如果上亿份热量集中到 1 平方厘米的面积,工作时散发的热量本身就可以把芯片烧毁。只有 MOS 管能在 1 平方厘米的空间内堆满上百万甚至上亿个。这是因为,当一个 MOS 管变小时,一切都会变得更好:功耗下降,与功耗相伴的发热也随之降低,甚至每一个管的速度也会变得更快。

MOS 管尺寸缩小后,一切都变好了。这是怎么做到的?

让我们在电脑中做个虚拟的实验。这个窗口代表芯片中最小的电路。要想让它正常工作,你需要先连接上电源电压和地,你可理解成接上了正极、负极,给这块电路通上了电。这时给一个输入信号,就会得到相应的输出。

电路中只有两个 MOS 管,查看这个电路的细节,两个 MOS 管被金属连接在一起。我们刚刚接好的电源电压和地,以及输入和输出是分别加载在这四个位置的。

让我们再次输入一串 0 和 1 ,也就是交替输入高低两种电压。屏幕上监测了最终输出的电压和电流大小。可以看到,大多数时候电流是 0,没有电流就没有功耗,不费电也不发热。当输入信号被处理,或者说被计算的瞬间,才会在瞬间产生一个尖峰电流,此时电路才会耗电、发热。

功耗的大小就是电压和电流两条曲线相乘,也就是这个面积。现在,我们来修改下 MOS 管的尺寸,也就是让沟道长度变得更小。电压曲线变得更方正,电流更锐,代表功耗的面积也变小了。

真不错,但其实我们还可以更进一步。

减小尺寸还意味着你不需要太大的电压来驱动它。我们还可以适当减小电源电压,功耗又可以再降低更多。这还带来另一个隐形的好处,缩小尺寸让输出信号更锐利,于是我们有足够空间主动地提升开关切换的频率,也就是让芯片算得更快。

晶体管与算力的大爆发

| 集成电路时代

MOS 管完美解决了空间上放不下的问题。但要打破算力锁死,让每个人都用得起,晶体管还要变得更便宜。

这难不倒技术爆发的二十世纪。在 1957 年,一个计算机系统需要大量电子管手工连线,这已经让工程师非常苦恼。晶体管时代,数量更多,连线更复杂。一个一个地生产晶体管再连接到一起,是不可能完成任务。此时,罗伯特·诺顿·诺伊斯提出了一种新的工艺,催生了一种新的制造方式,我们称它叫集成电路。

集成电路的做法则是直接在一整个硅晶体表面,同时做出全部的晶体管与连接它们的导线。今天一个小方块上就有 200 亿个晶体管,它们是被同时生产出来并连接在一起的。

从 2000 个到 200 亿个,数量增加千万倍,但工序,也就是制造的难度只增加几倍。这使得生产效率极大地提升,每一个晶体管也变得更便宜,这是一个简单的经济学问题。正如 Intel 创始人戈登摩尔提出的那个著名的摩尔定律:「集成电路上的晶体管将每两年翻一番」

集成电路工艺的演进让晶体管更小、更多、更廉价,算力在此刻有了一个明晰的标准,那就是单位面积的集成电路上拥有的晶体管数量。算力像空气和水一样变成每一个人都可以轻松获取的资源。每个人都美好的未来。

然而,这场晶体管与算力的大爆发好像不会一直持续下去。

1999 年,一场关于「晶体管不再会变小」「算力将被锁死」的论调开始在人群中蔓延。

1999 年,发生了什么,为什么人们如此焦虑?

鬼魅般的漏电

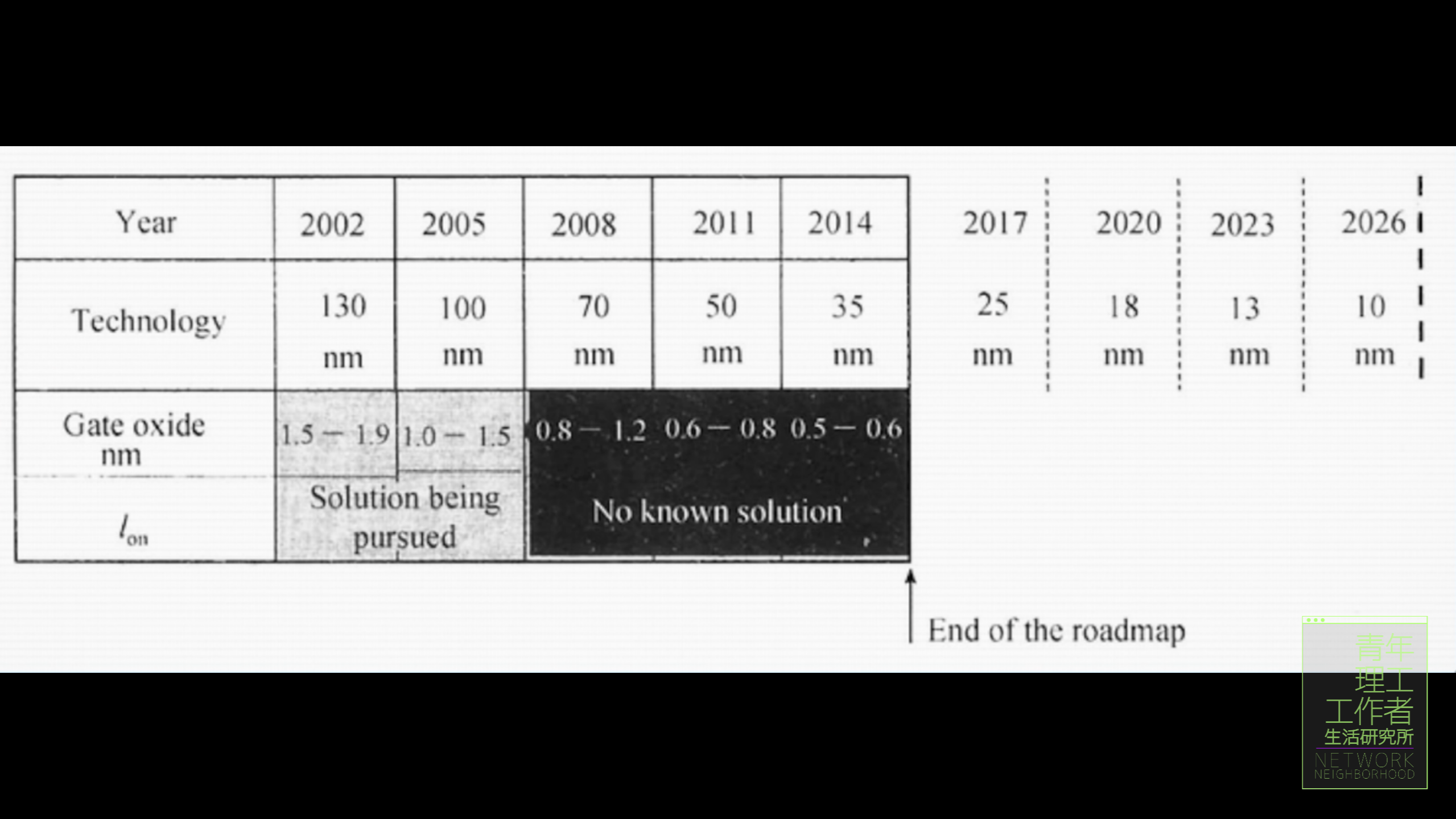

焦虑的源头是这样一个表格,上面赫然写着「技术路线的终结」。

表格上有两行数据,分别是导电沟道的长度和绝缘体的厚度。把这组数画在一个坐标系里,能看出它们高度关联。导电沟道越短,绝缘体的厚度就要越薄。这似乎是个很重要的信息。

翻了几本书,我发现它们在解释这件事时都提到了同一个词——漏电。

漏电是什么?拿平面型 MOS 管举例。源极接地,也就是 0V;漏极接正的电源电压,假如说是 5V;绝缘体外的栅极接输入信号,也就是在 0V 和 5V 之间来回跳转,它们分别代表信号0,信号 1。这便是 MOS 管日常的工作状态。

当尺寸小的一定程度时,半导体会误把漏极的电压当成栅极的电压,形成持续的漏电流。这会让晶体管一直处于半导通的状态,持续耗电,让整体的功耗增加。增加功耗其实还是小事情,当导通与关断变得不鲜明,它表示的 0 和 1 也变得模糊不清,整个功能都乱套了。

解决办法是让有用的电压信号重获控制权,也就是让中间的绝缘体变薄,让栅极电压距离半导体近一些。更薄的绝缘体让栅极的信号距离更近,对抗漏极电压干扰的能力越强。

这时我们终于能看懂这份报告。

为了把导电沟道做得更窄,我们不得不把绝缘体的厚度额外打薄一些。让栅极距离导电沟道更近,抵过漏极对导电沟道的影响。

当绝缘体厚度接近一层原子的厚度时,就不能变得更薄了,也就是零点几纳米。此时对应的沟道长度是 35 纳米。也就是这种晶体管的终结。

这就是各大芯片公司的工程师与科学家十年探索无果后的结论。二十世纪八十年代,大家发现当工艺接近 35 纳米的时候,晶体管就不能再变小了。各种方案陆续登场,或是技术或是成本的原因,这些方案又被一次次抛弃。大家预测,2010 年工艺将来到 35 纳米,也就是算力的末日。

当然,2023 年的我们知道这件事并没有发生,这二十年来一块芯片上晶体管的数量依然以很高的速度增加。这之间又发生了什么?

迟到的算力末日

2010 年是一个关键的时间点。如果晶体管没有走向终结,那我们只需要看看 2010 年前后各大处理器厂商都在干什么就好了。

看完几场发布会与报导,一个关键词浮出水面——FinFET,这似乎是一个很格外重要的东西,它的背后是一个华人的名字——胡正明。

现在回看胡正明的工作其实并不复杂,他只回答了一个问题:漏电流会从哪里经过呢?你或许会问,这有什么值得研究的?既然导通时电流从导电沟道经过,漏电不也该发生在这里吗?

还真不是。

胡正明给出了一个不一样的结论——经过计算和模拟,漏电发生的位置比人们猜想的更深。就像下方的示意图,颜色越红,代表电流密度越大,可以看到漏电发生在更深的地方,而不是导电沟道附近。

所以之前的科学家努力的方向好像都不太对,如果漏电发生在深处而不是表面,将绝缘体做薄,栅极有用的信号确实会距离漏电的地方更近一些,但已经不足以和干扰拉开差距,再薄的氧化物也鞭长莫及。

好用的办法都失效了,减小尺寸,让绝缘体变薄,都无法解决漏电的问题。于是一个更离谱的想法诞生了。漏电发生在半导体深处,那如果更深的地方没有半导体存在,漏电流不久也跟着消失了吗?

把这个看似天真到有点傻的办法转变成正经的科学研究就是它:

这里是半导体,可以看到,半导体越薄,这个图中的颜色就越绿、越蓝,代表漏电流越小。

接下来,就是要把这个想法变成现实。

漏电,只要足够薄就能解决。在三维软件中将一块半导体变薄十分简单。但现实中,极其复杂,并且十分昂贵。怎样把这个薄薄的东西造出来,还要保证足够便宜呢?一个诡异的想法在胡正明的大脑中诞生。

还是原来厚厚的平面型晶体管,如果能把上面这一层掀起来,掀个 90 度,立在硅表面,一个超薄晶体管就形成了。只不过这个超薄晶体管是立着放的。源极、漏极、栅极、导电沟道,还和原来一样。

这个尺寸,也就是晶体管的厚度,决定了漏电流的大小。像现在这么薄时,漏电流就可以忽略了。

这种方案,还能在有限空间内放下更多的超薄晶体管。我们可以把这个薄片复制几份,像这样一起立在硅上。

既然晶体管已经立起来了,它们的栅极和其他金属也要找个新位置。只需要直接盖上一条金属,当做它们共同的栅极,4 个立起来的晶体管就完成了。令人难以置信的是,造这样一个奇葩的结构,要比直接减薄的方案更便宜,也更容易。

要理解这个反常的结论,我们首先要探寻厚厚的老式平面型晶体管其中的一个细节——STI(Shallow Trench Isolation浅槽隔离)。这个名称其实还挺形象的,其实就是在硅片上挖许多槽,用绝缘的氧化物填满。厚厚的老式平面型晶体管生长在这些槽之间。这样一来绝缘槽就能将晶体管隔离起来,防止两个晶体管之间相互干扰。

既然已经挖槽了,那么挖的稍微密一些,深一些,在工艺上也不会太难做。于是,一个个高高立起的薄片形成了。

仔细看,如果你不把挖下去的地方当成槽,而是把这个突起的薄片当成一个立着的薄晶体管,胡正明的想法就实现了,还是我们熟悉的栅极、源极、漏极,而导电沟道在这里。这里越薄,漏电流就越小到可以忽略。

立起来的一个个超薄晶体管如同鱼鳍,人们给它起了一个形象的名字——FinFET,鳍式场效应晶体管。

FinFET 的想法在 1999 年诞生,十年后,平面型晶体管进入 32nm 的时代,正如当初的预言,这也是它最后一个时代。2011 年,第一批使用 FinFET 工艺的处理器问世,人们终于突破了 30 纳米的魔咒,进入了 20 纳米的时代。

值得注意的是,此后厂家宣传的 22 纳米、14 纳米、7 纳米、3 纳米,都不再代表导电沟道的尺寸。由于标准不一样,这些数字所衡量的位置没有统一的标准,同样是 7 纳米,大小也许完全不一样, 5 纳米也可能比 7 纳米更大,很难说谁比谁更先进。

今天,各大厂商在 FinFET 基础上缝缝补补,依然诉说着豪言壮语,续写着摩尔定律的传奇。但随着尺寸进一步减小,漏电以及漏电之外的其他问题相继出现在 FinFET 上。FinFET 的尺寸极限也许并不遥远。我们迟早要面临与 1999 年类似的窘境,直到有一天,廉价的芯片再一次变成昂贵的巨物,个人拥有的算力再一次迎来停滞的威胁。

那么,人们该如何面对个人算力停滞的阵痛期呢?

阵痛期的人类

想到现如今的智能汽车产业,他们或许对芯片有着更多的需求。于是,我来到了红旗的芯片选型部门,打算亲自看看汽车芯片是什么样的。

「现在的芯片选型有没有算力不足的焦虑?」一见面,我就把问题抛向了红旗新能源智能网联工程师赵目龙。他告诉我,算力是当前智能驾驶、智能座舱等技术指标里的关键一项。不同于传统汽车,当前我们需要的算力是AI、GPU、CPU的算力,整个计算芯片的工作频率都会在 GHz 以上,未来很有可能要超过高端手机芯片的性能指标。

GHz 是什么样的概念?

传统汽车搭载的是多个微控制器(MCU),它们的算力很低,只能采集和控制汽车的运行状态,比如最重要的喷油控制。

而新能源车更像是一台飞驰的电脑,除了 CPU 本身的算力更强,更复杂,还包含了与自动驾驶相关的 AI 算力和图形算力。工作主频也达到 GHz,未来可能将超过手机。

今天,一辆红旗新能源车内就有超过 10 TOPS 的算力,而正在开发阶段的 500 TOPS 平台,将对 L3 高级别自动驾驶需求发起挑战。同时,1000 TOPS 平台也已进入规划阶段。通过算力预埋,一辆车的算力始终走在驾驶需求的前面。

这意味工程师可以在一辆车里完成更多的事情:L2+ 级自动驾驶;更高效、安全的中央化控制系统;以及座舱内定制化的交互体验。红旗新能源智能网联工程师李岩告诉我:「软件会承载更多的这种功能和需求,迭代速度也会更快。通过整体设计,未来这种功能的集成会越来越多,软件会变得越来越复杂。」

这次沟通让我收集到了一些乐观的信息:红旗对算力的规划和预埋让汽车变得比原来更聪明,而且这一过程似乎不会减慢。同时,芯片这个硬件本身也依然以很高的速度更新迭代。

于是我又产生了一个新的问题:在晶体管不会更小更多更快的前提下,能不能造出更便宜,算力还更强的芯片呢?

借着研究,我很荣幸和中国科学院计算技术研究所研究员、龙芯 CPU 首席科学家胡伟武取得了联系。更没想到的是,第一次见面,胡伟武就邀请我一起玩游戏,竟是为了测试龙芯 3A6000。

在胡伟武看来,3A6000(芯片)对我们国家来说是有里程碑意义的,标着着相同工艺下,国产芯片的性能跟 Intel 和 AMD 比不差了。跟 AMD 12 纳米的 Zen 和 Zen+ 比,四核比四核,单核比单核,相同工艺下,我们都不差。当然,我们是用设计提高性能的。

所以,在晶体管尺寸被锁死的未来,我们还可以通过更好的设计,继续提高芯片算力。

芯片设计,其实就是想办法把上百万个晶体管连起来,比如把这几个小电路相连,就得到了一个半加器。16 个半加器组合在一起就组成了一个 8 位加法器。然而,当我费半天劲把这个加法器做完时,已经花了一个小时。如果要把几百万个这样的小东西连接在一起,徒手画出真实的芯片电路,可能需要好几年。所以,设计处理器芯片的工程师通常是写代码。

那么,芯片是怎么被代码设计出来的呢?

这个电路可以做与非运算,对应的代码是它。

这个电路可以做 1 位加法,代码是这样。

更复杂的电路,就需要更多行代码。一块芯片一般需要几百万行代码。

不同的是,写代码的效率,要比画这样的版图高多了,关键是还能读得懂。

从代码到芯片还需要两步,先把代码翻译成这样的网表,是不是看起来更像个电路图了,这个过程叫逻辑综合,是电脑自动完成的。

网表中的每一块对应了这样一个小方块样子的电路,里面有几个或者十几个晶体管。线代表这些小电路之间是怎么被连接起来的。

接着,电脑会自动地把所有小电路一行行排列在一起,然后再根据网表中的连法,将这些小方块用一层层横平竖直的导电金属连接起来。这样一张芯片图纸就完成了。

了解了什么是设计。

性能更好的芯片,就是在写代码时,让它描述的电路本身处理数据更快;在把代码转换成实际版图时,让实际的电路面积更小,功耗更低。

从 3A5000 到 3A6000,干的就是这些事。虽然晶体管尺寸没有变化,但是更高效的代码、更优的布局和布线方案,带来了 1.6 倍的性能提升。

事实上,这么做的不仅是工艺被制约的中国。早在 21 世纪初,第一次算力危机前后,Intel 就把设计作为提升性能的重要一环。

2011 年,第一代 FinFET 暂时拯救了摩尔定律,经历了一次危机的厂商很清楚,这持续不了多久。

如果说晶体管工艺的演进是对物理极限的挑战,那么设计优化更像是一个数学问题。

200 亿个晶体管背后是无穷多种可能与几乎无限大的求解空间,最优解就藏匿其中,但没人知道它在哪。

今天这种解决方案很难让人放下对于算力锁死的担忧,我们尚不确定它是新的希望,还是另一个深渊。但知晓了这一切后,至少我更愿意相信,人类是可以解决当下这次算力危机的。

人类算力被锁死了吗

关于算力被锁死的思考并不是在今天突然产生的,它如同一把悬着的剑,伴随着晶体管诞生后的每一个时代,和每一个正在思考的人类。

所以,人类算力被锁死了吗?我的答案是,是与不是都不正确。我发现是人类的悲观、杞人忧天,才破解了每个时代的锁死。

至少我还愿意相信关于探索算力边界与寻找数学最优解的故事不会在我生活的时代戛然而止。

因为我们再也回不去那个算力天生就是被锁死的旧时代。

我们必须知道,我们终将知道。

Wir müssen wissen.Wir werden wissen.——David Hilbert

注:《青年理工工作者生活研究所》由腾讯视频尤里卡工作室制作出品。

> 下载 少数派 2.0 客户端、关注 少数派公众号,解锁全新阅读体验 📰

> 实用、好用的 正版软件,少数派为你呈现 🚀

如有侵权请联系:admin#unsafe.sh